3d drawing of encoder timing belt

Digital Circuits - Encoders

An Encoder is a combinational circuit that performs the reverse operation of Decoder. It has maximum of 2n input lines and 'n' output lines. It will produce a binary code equivalent to the input, which is active High. Therefore, the encoder encodes iinorth input lines with 'n' bits. It is optional to stand for the enable signal in encoders.

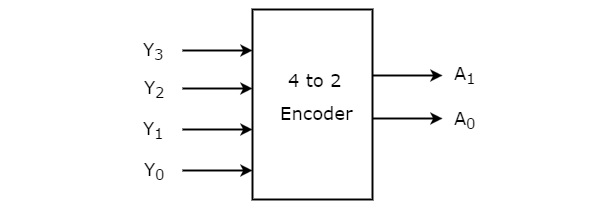

four to ii Encoder

Let iv to ii Encoder has four inputs Ythree, Y2, Y1 & Y0 and ii outputs A1 & A0. The block diagram of 4 to two Encoder is shown in the following effigy.

At whatsoever time, only one of these 4 inputs tin can be 'ane' in guild to become the respective binary code at the output. The Truth table of 4 to ii encoder is shown beneath.

| Inputs | Outputs | ||||

|---|---|---|---|---|---|

| Y3 | Y2 | Y1 | Y0 | Aane | A0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | i | ane |

From Truth table, we can write the Boolean functions for each output every bit

$$A_{one}=Y_{three}+Y_{two}$$

$$A_{0}=Y_{3}+Y_{1}$$

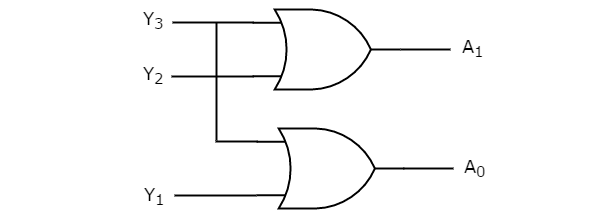

We tin implement the above 2 Boolean functions by using 2 input OR gates. The circuit diagram of four to ii encoder is shown in the following effigy.

The above circuit diagram contains 2 OR gates. These OR gates encode the four inputs with two bits

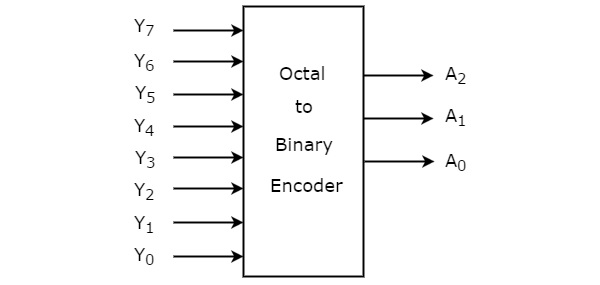

Octal to Binary Encoder

Octal to binary Encoder has eight inputs, Y7 to Y0 and three outputs A2, A1 & A0. Octal to binary encoder is nothing but 8 to 3 encoder. The cake diagram of octal to binary Encoder is shown in the following figure.

At any time, only one of these eight inputs can be '1' in club to get the corresponding binary code. The Truth table of octal to binary encoder is shown below.

| Inputs | Outputs | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Yseven | Y6 | Y5 | Yfour | Ythree | Y2 | Yone | Y0 | Atwo | A1 | A0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | one | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | one |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| one | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | ane | 1 |

From Truth table, nosotros can write the Boolean functions for each output as

$$A_{2}=Y_{7}+Y_{six}+Y_{5}+Y_{4}$$

$$A_{1}=Y_{7}+Y_{six}+Y_{iii}+Y_{2}$$

$$A_{0}=Y_{seven}+Y_{5}+Y_{3}+Y_{1}$$

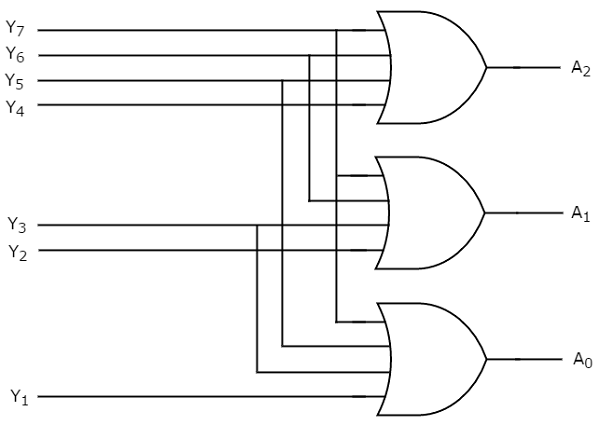

We tin implement the in a higher place Boolean functions past using four input OR gates. The excursion diagram of octal to binary encoder is shown in the post-obit figure.

The above circuit diagram contains three four-input OR gates. These OR gates encode the eight inputs with three bits.

Drawbacks of Encoder

Following are the drawbacks of normal encoder.

-

There is an ambiguity, when all outputs of encoder are equal to zero. Considering, information technology could be the lawmaking corresponding to the inputs, when just least significant input is one or when all inputs are zilch.

-

If more than than ane input is active Loftier, then the encoder produces an output, which may not be the right code. For example, if both Y3 and Y6 are 'ane', then the encoder produces 111 at the output. This is neither equivalent code corresponding to Ythree, when it is '1' nor the equivalent lawmaking corresponding to Y6, when it is 'i'.

So, to overcome these difficulties, we should assign priorities to each input of encoder. Then, the output of encoder will exist the (binary) code corresponding to the agile Loftier input(southward), which has college priority. This encoder is called as priority encoder.

Priority Encoder

A four to two priority encoder has iv inputs Y3, Y2, Y1 & Y0 and two outputs A1 & A0. Hither, the input, Y3 has the highest priority, whereas the input, Y0 has the everyman priority. In this case, even if more than than ane input is '1' at the same time, the output will be the (binary) lawmaking corresponding to the input, which is having higher priority.

Nosotros considered one more output, V in order to know, whether the code available at outputs is valid or not.

-

If at least 1 input of the encoder is 'ane', then the code available at outputs is a valid one. In this example, the output, V will be equal to 1.

-

If all the inputs of encoder are '0', then the lawmaking bachelor at outputs is not a valid one. In this case, the output, V volition be equal to 0.

The Truth table of 4 to 2 priority encoder is shown below.

| Inputs | Outputs | |||||

|---|---|---|---|---|---|---|

| Y3 | Yii | Y1 | Y0 | A1 | A0 | V |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | ane | x | 0 | 1 | 1 |

| 0 | 1 | x | ten | 1 | 0 | 1 |

| i | x | 10 | x | one | ane | one |

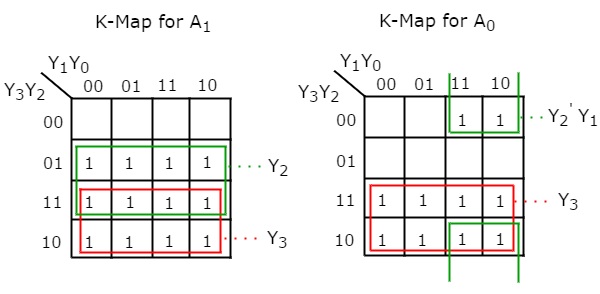

Utilise 4 variable K-maps for getting simplified expressions for each output.

The simplified Boolean functions are

$$A_{one}=Y_{iii}+Y_{2}$$

$A_{0}=Y_{3}+{Y_{ii}}'Y_{i}$

Similarly, we volition get the Boolean part of output, Five as

$$5=Y_{3}+Y_{2}+Y_{i}+Y_{0}$$

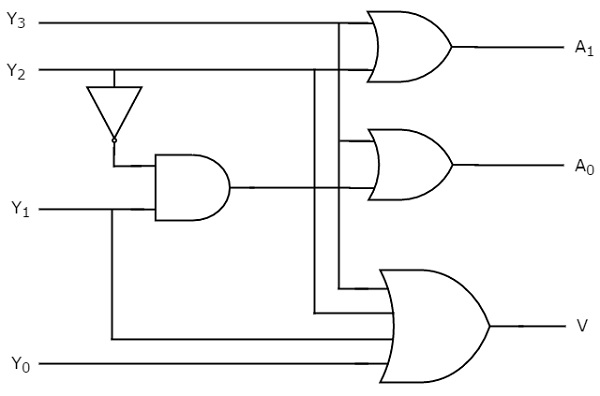

We can implement the above Boolean functions using logic gates. The circuit diagram of 4 to 2 priority encoder is shown in the following figure.

The above circuit diagram contains two 2-input OR gates, ane 4-input OR gate, one 2input AND gate & an inverter. Here AND gate & inverter combination are used for producing a valid code at the outputs, fifty-fifty when multiple inputs are equal to '1' at the same time. Hence, this excursion encodes the iv inputs with ii bits based on the priority assigned to each input.

Useful Video Courses

Video

Video

Video

Video

Video

Video

Source: https://www.tutorialspoint.com/digital_circuits/digital_circuits_encoders.htm

0 Response to "3d drawing of encoder timing belt"

Post a Comment